# Nanoscale pattern transfer for Templates, NEMs, and Nano-optics

Deirdre L. Olynick,<sup>a</sup> J. Alexander Liddle,<sup>b</sup> Bruce D. Harteneck, Stefano Cabrini, Ivo W. Rangelow<sup>c</sup> Lawrence Berkeley National Laboratory, Molecular Foundry<sup>d</sup> One Cyclotron Road, Mail Stop 67-2206, Berkeley, CA 94720

# ABSTRACT

Plasma etching is an enabling technology in nano optic, nanoelectronic devices, nano electro mechanical systems (NEMS) and nanoresolution templates for nano imprint lithography (NIL). With shrinkage, one must overcome significant challenges to meet the stringent profile and CD goals necessary for nanoscale applications. Using the example of Si nanoimprint template fabrication, we show how ion/sidewall/mask interactions can dominate feature profile evolution at the nanoscale and what to look for successful pattern transfer. Gas chopping or multiplexed etching, generally used for deep silicon etching, is often avoided at the nanoscale due to unacceptable undercut and sidewall scalloping. We demonstrate a multiplexed etching process in silicon with sub-5 nm amplitude scallops which is well suited for NEMS and nano optics applications and which reduces the deleterious role of ion/sidewall/mask interactions at the nanoscale.

## **1. INTRODUCTION**

Plasma etching has been a cornerstone of the semiconductor industry since the mid-1970's.<sup>1-3</sup> More recently, plasma etching, primarily of silicon and its compounds, has become a central process in micro and nanofabrication in areas such as nanoelectronics, microelectromechanical (MEMs) and nanoelectromechanical (NEMs) devices, nanophotonics, microfluidics<sup>2, 4, 5</sup> and nanoimprint lithographic templates.<sup>6</sup>

For many of these applications, profile shape, sidewall roughness, and CD uniformity is crucial. For instance, slight non-uniformities in etching profile and sidewall smoothness can modify the frequency response and reduce transmittance in photonic waveguides. Profile shape, sidewall roughness, CD, and CD-uniformity during etching is determined by a complex set of variables tuned through factors such as ICP-power density, reactor pressure, platen power, the surface chemistry at the etching interface, and mask composition and shape. In order to manipulate the profile evolution, it is important to understand the mechanism which dominates the shape. This necessitates careful studies because different underlying mechanisms can produce similar profile shapes.<sup>5</sup>

Experimental studies and modeling of profile development in sub-micron patterned Si undergoing Cl<sub>2</sub> and HBr dry etching have evolved over the last 10 years.<sup>5, 7-15</sup> For the purpose of precisely controlling profiles for imprint templates for nanodevices, we extended the experimental studies to the nanoscale regime.<sup>16, 17</sup> Here we discuss how ion interactions with the feature sidewalls and mask can completely dominate the overall feature shape as features shrink. Thorough studies as a function of feature size are required to identify the underlying mechanism and reduce effects which produce undesirable profiles. In addition, we show that by using techniques that rely less on high energy ion bombardment, for instance multiplexed etching typically used for high aspect ratio etching of silicon, we can produce nanostructures while mitigating the consequences of damaging ions on profile evolution and poor mask selectivity.

<sup>&</sup>lt;sup>a</sup> electronic mail: dlolynick@lbl.gov

<sup>&</sup>lt;sup>b</sup> current address: National Institute of Standards, Gaithersburg, MD

<sup>&</sup>lt;sup>c</sup> current address: Technical University Ilmenau, Ilmenau, Germany

<sup>&</sup>lt;sup>d</sup> Experimental work performed at the Center for X-ray Optics.

Micromachining Technology for Micro-Optics and Nano-Optics V and Microfabrication Process Technology XII, edited by Mary-Ann Maher, Harold D. Stewart, Jung-Chih Chiao, Thomas J. Suleski, Eric G. Johnson, Gregory P. Nordin, Proc. of SPIE Vol. 6462, 64620J, (2007) · 0277-786X/07/\$18 · doi: 10.1117/12.705033

# 2. PLASMA ETCHING FOR NANOIMPRINT TEMPLATE FABRICATION: THE ROLE OF IONS IN NANOSCALE PLASMA ETCHING

Nanoimprint is a promising emerging lithography for the patterning of nanostructures that can be exploited for nontraditional microelectronics applications such as photonic based technologies.<sup>6</sup> The theoretical resolution limit is in the range of the imprint polymer molecule and very small features, such as single walled carbon nanotubes have been replicated.<sup>18</sup> Furthermore, nanoimprint lithography can be considered an "amplifier" for other high resolution lithographic techniques such as electron-beam lithography. A 1 cm<sup>2</sup> e-beam printed template can be replicated approximately 50-70 times in an hour. This is crucial for nanoscience which requires large sample areas or a large quantity of samples (e-beam write time for a 50% coverage 1 cm<sup>2</sup> sample can be any where from 2-200 hours depending on resolution required). For example, nanoimprint lithographic replication of e-beam patterned samples is considered a promising pathway for patterned media development at sub-25 nm.<sup>19</sup>

In turn, plasma etching is an enabler for nanoimprint. First, with nanoimprint being a 1X replication process, the ultimate nanoimprint resolution depends on precise pattern transfer; topography defined in the template must maintain CD and release upon replication. In addition, every replica requires a critical plasma etching step to remove the residual polymer left behind by the imprint process without damaging the features of interest. Furthermore, pattern transfer on the replica often requires additional plasma etching steps.

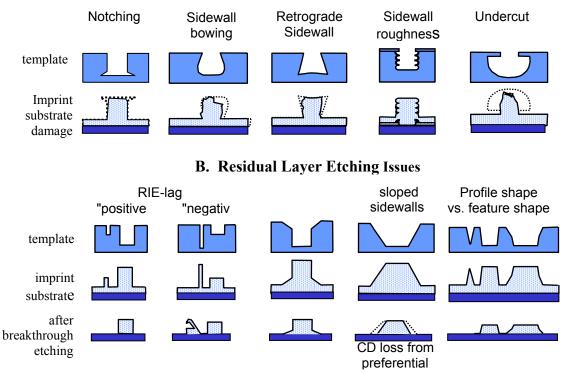

An optimally designed template will have feature profiles that resemble a perfect top hat function. This will allow proper release of the mold while also providing the best mask shape for breakthrough etching and subsequent pattern transfers. Deviations from the ideal profiles can produce defects in the replicas, problematic for the imprint process release and breakthrough steps. (Fig. 1). Retrograde profiles (sidewall features less than 90 degrees with the horizontal), which can develop while etching, can hinder mold release (Fig. 1A). Other types of etching profiles can promote CD changes during the imprint breakthrough-etching step (Fig. 1B). Precise CD control is very important for small features and has proven even more difficult as patterns become denser.

A. Substrate Release Issues

Fig. 1. Effects of template profile non-uniformities on imprinted profiles. A. Profiles which can affect release of the replicas. B. Profiles which can affect replicas during residual layer etching.

We have defined silicon nanoimprint templates electron beam patterned masks and dry etching using HBr chemistry. These templates were replicated using hot embossing for molecular electronics device fabrication.<sup>20</sup> In order to produce the best templates, three different electron beam patterned masks were studied: 20 nm of chromium, 100 nm of hydrogen silsesquioxane (HSQ, an inorganic, silicon based, electron beam resist available from Dow Corning), and a bilayer resist scheme of  $\sim$ 30 nm of HSQ on 100 nm of Shipley AZPN114. All etching work was conducted in an Oxford Plasmalab 380 system.

The activation energy for the interaction of bromine with silicon is 6 times higher than of fluorine<sup>21</sup> and contrary to fluorine based etching of silicon, ion bombardment is necessary to get acceptable etching rates. This allows highly anisotropic profiles to be etched without a sidewall passivant. However sidewall passivants are often introduced (for instance oxygen) to protect feature sidewalls from bombardment of off – axis ions (those that are oriented away from the surface normal).

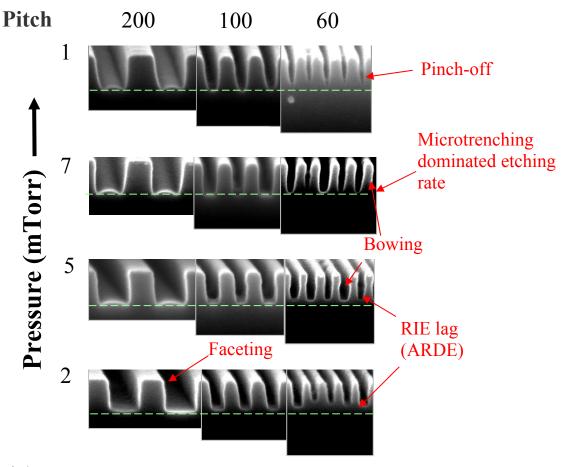

Figure 2 shows profiles defined in silicon using the chromium mask as a function of pressure and feature size. The recipe used was 20 sccm HBr, 60 W on the bottom electrode, 760 W on the ICP source, and 20 degrees C. Chamber pressure varied from 2-10 mtorr. The target feature size and pitch was 30 nm and 60 nm respectively. Many deviations from the ideal profile are apparent. At high pressures features are "pinched-off." That is, the trench narrows and etching rate slowed significantly. Bowing is apparent as pressure is lowered. This results in retrograde profiles that can be deleterious on imprint mold release. At the lowest pressures, there is noticeable faceting of the features.

Fig.2 A study of the effects of pressure and pitch on silicon feature profiles. Features were masked using 20 nm of chromium and etched in an ICP reactor with HBr chemistry

Interestingly enough, looking at the small features sizes alone, it is difficult to discern the underlying mechanisms for these profile non-uniformities. The same non-uniformities can result from numerous mechanisms<sup>5,22</sup> and it is important to discern the underlying cause so one can tune the process appropriately. Here, by looking at non-uniformities at multiple feature sizes, the influence of ions is readily apparent. For instance the etching rate is of the small features at 7 and 10 mtorr is actually dominated by ion interactions with the sidewalls. The 200 nm features have mictrotrenches (small trenches etched deeper than the bulk due to the reflection of ions from the sidewalls to trench bottoms where they subsequently etch) at pressures of 5, 7, and 10 mtorr. Although microtrenching is not apparent at the 60 nm pitch features, the etching rate is strongly influenced by the ion-sidewall interactions which cause the microtrenches on the larger features. (Fig. 2, 7 mtorr - line drawn across features show the microtrench etching rate at 200 nm pitch is the same etching rate for the features at 60 nm pitch). At smaller features sizes, bowing can manifest from the ions reflecting to the opposing sidewall.

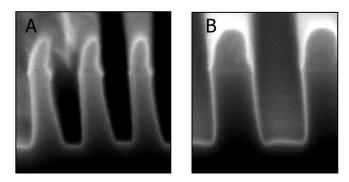

We have demonstrated the role ion flux can play in the developing nanoscale profile as a function of pressure and feature size with a thin chromium mask. Different mask types can strongly influence profile evolution. Fig. 3 shows silicon

features etched with the bilayer mask (HSQ on polymer). The mask fell over during etching process and consequently alters the ion flux and interaction with the sidewall. Asymmetric trench profiles are produced. Profile simulations of chlorine etching of silicon show that slight changes in mask shape/ inclinations angles have dramatic influence on mictrotrench formation.<sup>15</sup> Furthermore, the mask is not conductive and mask charging can play a significant role in the ion/sidewall interactions. The reader is directed to Ref. 4 for a more thorough treatment of plasma induced charging and the effects on profile evolution. Needless to say, this is an important issue at the nanoscale where shading can occur at very short etch times because higher aspect ratios are reached soon into the etch.

Similar nonuniformities are apparent in the etching of 60 nm pitch features in silicon using an HSQ mask (Fig. 4., HSQ was originally 100 nm thick). Note that the profiles are much straighter on the outside

Fig. 3. Silicon features etched using a bi-layer mask (HSQ on polymer) and HBr chemistry. Polymer has fallen over during the etching process. The asymmetric tilting of the mask results in asymmetric profiles. A) 100 nm pitch features. B) 200 nm pitch features.

lines where ion and electron shading are reduced. Furthermore, one can see bowing is more pronounced opposite faceted mask faces. Feature charging and/or ion reflections from faceted mask to the opposing sidewall is involved in profile evolution playing a role. HSQ/silicon selectivity is approximately three times higher than the resist/silicon selectivity and ion reflections from the mask can be more significant.

Fig. 4. Silicon features etched using HSQ mask (originally 100 nm) and HBr chemistry. Features pitch is 60 nm. Profiles are much straighter on the outside of the comb structure (A) where there is little ion and electron shading. Masks are more faceted (B, a black line is drawn to accentuate the facet) and features more bowed (C) on trenches close to the outside potentially resulting from feature charging and/or reflections from the faceted mask.

It is clear from these studies that ion/mask/sidewall interactions play a huge role in the developing profile and often cause unwanted profile features. These profile deviations show up with very short etching times and can be a significant portion of the overall profile. In order to minimize the effect of ions, our group investigated etching chemistries which are less dependent on higher energy ion bombardment.

# 3. GAS CHOPPING FOR NANOSCALE ETCHING

Fluorine etching of silicon has advantages over bromine and chlorine based etching because high etching rates can be achieved without the need for high-energy ion bombardment. The reaction between silicon and fluorine is exothermic and anisotropy is controlled by finding the right synergy of spontaneous chemical etching, deposition of a passivation species to protect the sidewall (often fluorocarbon based), and ion bombardment removing the passivant on the bottom of the features.

The idea of gas-chopping deep reactive ion etching (GCDRIE),<sup>23, 24, 25</sup> sometimes called multiplexed deep reactive ion etching, is to temporally separate etching and deposition, in order to carry out each step under optimised conditions. With this approach, first an isotropic etching step with  $SF_6$  plasma is carried out for a duration of a few seconds to minutes, creating an isotropic etch profile of a depth of a few hundreds of nanometers. The second step is deposition of a passivation layer (usually a fluorocarbon gas), to prevent further attack of the area already etched. The duration for this second step depends on the passivation efficiency and is usually shorter than the etching step. These two steps are repeated, alternating throughout the complete etching process. The result is an overall anisotropic profile with sidewall angles ranging from slightly positive to vertical to negative (retrograde) but with high sidewall scalloping or roughness.

In combination with an ICP reactor, gas chopping offers the unique opportunity to control almost independently, the energy and the density of the ion and neutral flux, with minimum overlap between the etching and passivation steps, as the precursors are switched. Consequently, it has become one of the most important processes for MEMS fabrication.

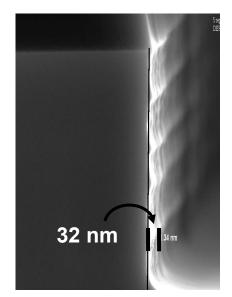

The challenge is transferring such a process to nanoscale features. Typically scalloped sidewalls develop as the process is switched between etching and deposition. Ayon et. al.'s characterization of a multiplexed etcher mentioned 50 nm as their lower limit for scallop amplitude.<sup>26</sup> Figure 5 shows a profile achieved with a modified gas chopping Here, the sidewall scalloping has process. amplitude of 30 nm -- perfectly acceptable for typical MEMS applications where feature sizes are in the micron size regime. Of course, dense sub-50 nm features would be totally eroded with sidewall scalloping of this magnitude. Furthermore, for photonics applications, smoother sidewalls are important for higher transmission, low loss devices.

Fig. 5. Scallop amplitude is 32 nm on silicon features etched using a modified multiplexed-process. Scallops of this magnitude would preclude the formation densely packed nanofeatures

Commercial tool vendors are striving to minimize the scallops.<sup>27</sup> A few groups have reduced the sidewall RMS roughness (measured using AFM) below 10 nm.<sup>28-30</sup> Liu, et. al. demonstrated roughness on the order of 9 nm and Chabloz et. al. demonstrated roughness below 4 nm. However, the 4 nm roughness achieved by Chabloz et. al. was accompanied by 100 nm of undercut, precluding the formation of dense nanoscale features. Sidewall scallops are smoothed and the walls are laterally etched as the number of etch/depth cycles increase.<sup>31</sup> Chen, et. al. paper did not

disclose recipe or profile information for their smooth sidewall process; thus, it is not clear whether this process was associated with a large undercut.

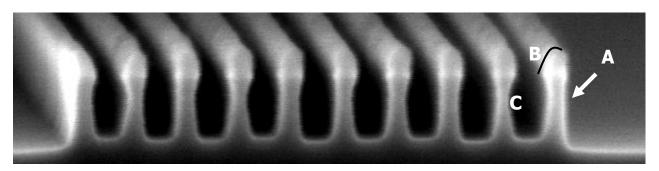

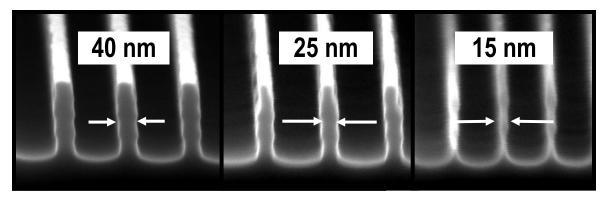

Fig. 6 . Nanoscale features etched using new gas chopping process (Etching step: SF<sub>6</sub>/Ar, Deposition Step: CHF<sub>3</sub>/CH<sub>4</sub>). Scallop amplitude is below 5 nm and feature profiles are self-similar.

With a new gas chopping process we have successfully reduced scalloping at the onset of etching to allow successful etching of nanoscale features. Figure 6 shows sub-50 nm nanofeatures etched using a gas chopping process.<sup>32</sup> Here, the peak-to-valley measurements of the sidewall scallops are less than 5 nm; RMS roughness should be decidedly less. Furthermore, feature profiles are self-similar as feature sizes decrease. This is contrary to that observed using the HBr process where ion/sidewall reflections dominate the profile. The etching step used SF<sub>6</sub>/Ar chemistry (for example, SF<sub>6</sub> 4-7 sccm, Ar 7 sccm, 8 mtorr chamber pressure, 600 W ICP power, 40 W RF power, DC bias -100 V, wafer temp 10 °C)

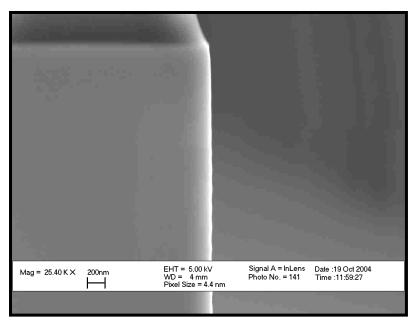

Fig. 7. Micron-sized feature etched using new gas chopping process.

and the passivation step uses CHF<sub>3</sub>/CH<sub>4</sub> chemistry (for example, CHF<sub>3</sub> 15 sccm, CH<sub>4</sub> 7 sccm, 35 mtorr chamber pressure, 600 W ICP power, 15 W RF power, DC bias -32 V, wafer temp 10 °C). Etching parameters such as step times, pressure, and flow ratios were tuned until small scallops were achieved. One key parameter for successful etching is the conditioning of the chamber with the alternating process. XPS analysis of the passivant composition shows dramatic changes between the conditioned chamber and the unconditioned chamber. The sidewall film on the features etched after chamber conditioning contain a relatively higher concentration of CF<sub>2</sub>, a denser film which has better resistance to etching by free fluorine. This process is suitable for deeper silicon etching as well (Fig. 7). This process produces more RIE lag than the proceeding HBr processes, however the etching stops can mitigate this issue. Further process details can be found elsewhere.33

## 4. SUMMARY

We have demonstrated issues with nanoscale pattern transfer using HBr etching of silicon. Ion interactions with the sidewalls and masks dominate in the etching profile evolution. Profiles are often not self-similar as feature sizes shrink and several sizes must be investigated to understand the underlying mechanisms. Ion angular distributions, feature charging, mask angle, mask chemistry, and mask aspect ratio are all playing a role in the evolving profile. In addition, aspect ratio effects become an issue at shallower etching depths because feature sizes are small. Not only will these issues be important for the etching of silicon nano-features with HBr, but also for other processes that require ion bombardment for the etching to occur (i.e. fluorocarbon based etching of SiO2).

Using a new approach to nanoscale pattern transfer, gas chopping, we take advantage of the fact that fluorine etching of silicon does not require high ion flux for activation. With this multiplexed process, we produce high aspect ratio nanoscale features without the deleterious ion/sidewall interactions we observed with HBr etching chemistry. In general, more novel approaches will need to be explored to meet the stringent requirements of pattern transfer at the nanoscale.

#### Acknowledgements

This work was supported by the Director, Office of Science, Office of Basic Energy Sciences, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231 and by the Assistant Secretary for Energy Efficiency and Renewable Energy, Office of Building Technology, State, and Community Programs, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

## References

- 1. J. L. Cecchi and L. M. Cecchi, "Plasma Science and technology: 50 years of progress", *J. Vac. Sci. Technol. A*, **21**, s129-s130, 2003.

- 2. C. Cardinaud, M.-C. Peignon and P.-Y. Tessier, "Plasma etching: principles, mechanisms, application to micro- and nano-technologies", *Applied Surface Science*, **164**, 72-83, 2000.

- 3. M. Sugawara, "Preface", *Plasma Etching: Fundamentals and Applications*, M. Sugawara, v-vi, Oxford University Press, Oxford, 1998.

- 4. R. J. Shul and J. G. Fleming, "Bulk Si Micromachining for Integrated Microsystems and MEMS Processing", *Handbook of Advanced Plasma Processing Techniques*, R. J. Shul and S. J. Pearton, 419-457, Springer-Verlag, Berlin, 2000.

- 5. I. W. Rangelow, "Critical tasks in high aspect ratio silicon dry etching for microelectromechanical systems", J. Vac. Sci. Technol. A, 21, 1550-1562, 2003.

- 6. L. J. Guo, "Recent progress in nanoimpint technology and its applications", J. Phys. D, 37, R123-R141, 2004.

- 7. C. Cheng, A. K. V. Guinn and V. M. Donnelly, "Mechanism for anisotropic etching of photoresist-masked, polycrystalline silicon in HBr plasmas", *J. Vac. Sci. Technol. B*, **14**, 85-90, 1996.

- 8. H. H. Hwang, M. Meyyappan, G. S. Mathad and R. Ranade, "Simulations and experiments of etching of silicon in HBr plasmas for high aspect ratio features", *J. Vac. Sci. Technol. B*, **20**, 2199-2205, 2002.

- 9. A. P. Mahorowala and H. H. Sawin, "Etching of polysilicon in inductively coupled Cl/sub 2/ and HBr discharges. III. Photoresist mask faceting, sidewall deposition, and microtrenching", *J. Vac. Sci. Technol. B*, **20**, 1077-1083, 2002.

- 10. A. P. Mahorowala and H. H. Sawin, "Etching of polysilicon in inductively coupled Cl/sub 2/ and HBr discharges. IV. Calculation of feature charging in profile evolution", *J. Vac. Sci. Technol. B*, **20**, 1084-1095, 2002.

- 11. A. P. Mahorowala, H. H. Sawin, R. Jones and A. H. Labun, "Etching of polysilicon in inductively coupled Cl<sub>2</sub> and Hbr discharges. I Experimental characterization of polysilicon profiles", *J. Vac. Sci. Technol. B*, **20**, 1055, 2002.

- 12. L. M. Vyvoda M.A., Graves D. B., "Hardmask charging during Cl-2 plasma etching of silicon", J. Vac. Sci. Technol. A, 17, 3293-3307, 1999.

- L. M. Vyvoda M.A., Graves D. B., Lee H., Malyshev M.V., Klemens F.P., Lee J.T.C., Donnelly V.M., "Role of sidewall scattering in feature profile evolution during Cl-2 and HBr plasma etching of silicon." *J. Vac. Sci. Technol. B*, **18**, 820-833, 2000.

- L. H. Vyvoda M.A., Malyshev M.V., Klemens F.P., Cerullo M., Donnelly V.M., Graves D.B., Kornblit A., Lee J.T.C., "Effects of plasma conditions on the shapes of features etched in Cl2 and HBr plasmas. I. Bulk crystalline silicon etching", *J. Vac. Sci. Technol. A*, 16, 3247-3258, 1998.

- 15. H. Hoekstra, Robert J. and M. J. Kushner, "Microtrenching resulting from specular refection during chlorine etching", J. Vac. Sci. Technol. B, 16, 2102-2104, 1998.

- 16. D. Olynick, J. A. Liddle and I. W. Rangelow, "Profile evolution of Cr masked features undergoing HBr-inductively coupled plasma etching for use in 25nm silicon nanoimprint templates", *J. Vac. Sci. Technol. B*, **23**, 2073-2077, 2005.

- 17. D. L. Olynick and I. W. Rangelow, "Nanoimprint mold fabrication at 30 nm: silicon nanopatterning using HSQ and polymer resist masks and HBR plasma chemistry", 28-29, 2004 AVS 5th Internation Conference on Microelectronics and Interfaces, Santa Clara, CA, 2004.

- F. Hua, A. Gaur, Y. Sun, M. Word, N. Jin, I. Adesida, M. Shim, A. Shim and J. A. Rogers, "Processing dependent behavior of soft imprint lithography on the 1-10 nm scale", *IEEE Transactions on Nanotechnology*, 5, 301-307, 2006.

- E. A. Dobisz, T.-W. Wu, T. R. Albrecht, Z. Z. Bandic, M. Best, D. Kercher, H. Yang, T. Thomson, O. Hellwig and B. Terris, "Nanofabrication for Patterned Media", 333, The 50th International Conference on Electron, Ion, and Photon Beam Technology and Nanofabrication, Baltimore, MD, 2006.

- W. Wu, G.-Y. Jung, D. L. Olynick, Z. Li, J. Straznicky, D. A. A. Ohlberg, X. Li, S.-Y. Wang, W. M. Tong and R. S. Williams, "One kilobit Cross-bar Molecular Memory Circuits at 30 mn Half Pitch Fabricated by a Double-layer Nanoimprint Lithography (NIL) Process", *Appl. Phys. A*, 80, 1173-1178, 2005.

- 21. Z. H. Walker and E. A. Ogryzio, "Rate constants for the etching of intrinsic and doped polycrystalline silicon by bromine atoms", *J. Appl. Phys.*, **69**, 2635-2638, 1991.

- 22. R. A. Gottscho, C. W. Jurgensen and D. J. Vitkavage, "Microscopic uniformity in plasma etching", J. Vac. Sci. Technol. B, 10, 2133-2147, 1992.

- 23. K. Tsujimoto, S. Tachi, K. Ninomiya, K. Suzuki, S. Okudaira and S. Nishimatsu, 229, IEEE 18th Int. Conf. S. St. Devices and Materials, Tokyo, 1986.

- I. W. Rangelow, "High Resolution Tri-Level Process by Downstream-Microwave RF-Biased Etching" Proc. of Microelectronic Processing Integration, , SPIE vol.1392 (1990) pp.180-184.

- 25. F. Laermer and A. Schilp, "Method of anisotropically etching silicon", U.S. Patent 5501893.

- 26. A. A. Ayon, R. Braff, C. C. Lin, H. H. Sawin and M. A. Schmidt, "Characterization of a time multiplexed inductively coupled plasma etcher", *J. Electrochem. Soc.*, **146**, 339-349, 1999.

- 27. S. Lai, D. Johnson, R. Westerman, J. Nolan, D. Purser and M. Devre, "Scalloping Minimization in Deep Si Etching on Unaxis DSE Tools", *Proceedings of SPIE*, **4979**, 43-50, 2003.

- 28. H.-C. Liu, Y.-H. Lin and W. Hsu, "Sidewall roughness control in advanced silicon etch process", *Microsyst. Technol.*, **10**, 29-34, 2003.

- 29. M. Chabloz, Y. Sakai, T. Matsuura and K. Tsutsumi, "Sidewall roughness control in advanced silcion etch process", *Microsyst. Technol.*, **6**, 86-89, 2003.

- K.-S. Chen, A. A. Ayon, X. Zhang and S. M. Spearing, "Effect of Process Parameters on the Surface Morphology and Mechanical Performance of Silicon Structures After Deep Reaction Ion Etching (DRIE)", J. Microelectromech. S., 11, 264-275, 2002.

- J.-H. Min, G.-R. Lee, J.-K. Lee, S. H. Moon and C.-K. Kim, "Dependence of bottom and sidewall etch rates on bias voltage and source power during the etching of poly-Si and fluorocarbon polymer using SF<sub>6</sub>, C<sub>4</sub>F<sub>8</sub>, and O<sub>2</sub> plasmas", *J. Vac. Sci. Technol. B*, 22, 893-901, 2004.

- D. L. Olynick, I. W. Rangelow and W. L. Chao, "Etching Radical Controlled Gas Chopped Deep Reactive Ion Etching", U.S. Patent 11/421958.

- 33. D. L. Olynick, J. A. Liddle and I. W. Rangelow, "Multiplexed etching for sub-20 nm features and smooth sidewalls", *Nanotechnology*, submitted 2007.