## Electrostatic Force Assisted Exfoliation of Prepatterned Few-Layer Graphenes into Device Sites

NANO LETTERS

2009 Vol. 9, No. 1 467-472

Xiaogan Liang,\* Allan S. P. Chang, Yuegang Zhang, Bruce D. Harteneck, Hyuck Choo, Deirdre L. Olynick, and Stefano Cabrini

Molecular Foundry, Lawrence Berkeley National Laboratory, 1 Cyclotron Road, Berkeley, California 94720

Received November 19, 2008; Revised Manuscript Received December 1, 2008

## **ABSTRACT**

We present a novel fabrication method for incorporating nanometer to micrometer scale few-layer graphene (FLG) features onto substrates with electrostatic exfoliation. We pattern highly oriented pyrolytic graphite using standard lithographic techniques and subsequently, in a single step, exfoliate and transfer-print the prepatterned FLG features onto a silicon wafer using electrostatic force. We have successfully demonstrated the exfoliation/printing of 18 nm wide FLG nanolines and periodic arrays of 1.4  $\mu$ m diameter pillars. Furthermore, we have fabricated graphene nanoribbon transistors using the patterned graphene nanoline. Our electrostatic force assisted exfoliation/print process does not need additional adhesion layers and could be stepped and repeated to deliver the prepatterned graphitic material over wafer-sized areas and allows the construction of graphene-based integrated circuits.

Recently, few-layer graphene (FLG) has been extensively studied as a material for making future electronic devices. FLG has exceptional properties, such as high carrier mobility (up to 20000 cm<sup>2</sup>/(V s)), high saturation velocities, a stable two-dimensional (2D) crystal structure, potential to realize ballistic transport at room temperature, and processing compatibility with state-of-the-art silicon technology. 1-3 Graphene-based electronic devices have been fabricated to study its superior transport properties.<sup>4-9</sup> Two of the challenges to making commercially viable graphene-based electronics are incorporating FLG material over large areas and fabricating nanoscale features to achieve the desired electronic properties (e.g., to open band gap in the electronic structure of graphene). Several approaches have been attempted to produce graphene for large area electronics, including epitaxial growth, 10-13 transfer-printing, 6,14 and solution-based deposition. 15,16 At the same time, efforts have been made to tailor graphene sheets into nanoscale features (e.g., nanoribbons). 8,17-19 Obviously, a method to simultaneously achieve nanoscale features over large areas would be a benefit to graphene-based electronics fabrication.

In this Letter, we demonstrate a novel micro and nano fabrication process for exfoliating and printing FLG over large areas, termed electrostatic force-assisted exfoliation of prepatterned graphene (EFEG). In this approach, ordered nano- and microscale FLG features are exfoliated from a prepatterned, pristine, HOPG surface and printed on a regular

semiconductor substrate (e.g., Si) by applying an electrostatic force. Such electrically exfoliated FLG flakes can be used to make working transistors showing good performance. In the future, this novel technique in combination with other nanolithography approaches may be employed to fabricate graphene-based large-scale integrated (LSI) circuits.

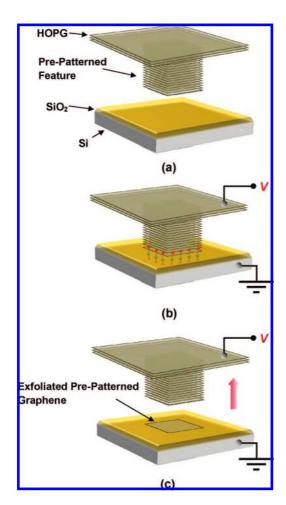

Figure 1 shows the schematic flowchart of electrostatic force assisted exfoliation of graphenes (EFEG). First, nanometer and micrometer scale relief features are patterned on the surface of a highly oriented pyrolytic graphite (HOPG) disk by using lithographic techniques followed with reactive ion etching (RIE) (Figure 1a). This structured HOPG disk serves as a template and is brought into contact with a SiO<sub>2</sub>/ Si substrate. A voltage between HOPG and semiconducting Si produces an electrostatic attraction force acting between the surface of prepatterned graphitic features and the silicon substrate (Figure 1b). As the HOPG template is vertically moved away from the substrate, the electrostatic force exfoliates the prepatterned few-layer graphenes and attaches them onto the SiO<sub>2</sub> surface (Figure 1c). The thin screening depth in HOPG (less than 0.5 nm) assures that the electrostatic force in the EFEG process acts only on the outmost graphene monolayers during each exfoliation/print cycle.<sup>3</sup> Such a highly localized drag force can modify the flatness or morphology of the outmost graphene layers and make them conformal to the flat substrate, but it barely affects the rest of the graphene layers in the graphite bulk. As a result, the boundary between electrically dragged graphene layers

<sup>\*</sup> Corresponding author, xliang@lbl.gov.

**Figure 1.** Schematic flowchart of electrostatic force assisted exfoliation of prepatterned few-layer graphenes (EFEG), which includes (a) initial setup with a HOPG template bearing prepatterned relief features, (b) application of a voltage between the HOPG template and the Si substrate after they are brought into contact, and (c) exfoliation of prepatterned few-layer graphenes by electrostatic force as the HOPG template is separated from the substrate. In EFEG, due to the thin screening depth in graphite (<0.5 nm), only several outmost graphene monolayers are dragged by the electrostatic force, preferably leading to a thin exfoliation thickness of FLGs.

and the rest of the layers likely serves as an exfoliating site because of modified interlayer spacing and accordingly weakened binding force. Therefore, it is expected that the EFEG process favorably produces thin exfoliated FLG flakes. The pristine FLG features, once exfoliated and printed onto substrate surface, can remain the original pattern arrangement predefined on the HOPG template. This exfoliation/print approach does not need any additional adhesive layer and could be repeated to print prepatterned graphitic features over the whole wafer area. Furthermore, with using prepatterned align marks, EFEG could also be used to place graphene nanostructures into specific locations with nanometer scale precision.

For the EFEG process, HOPG disks (SPI, Inc., 1 cm<sup>2</sup>) were exfoliated with flexible Scotch tape to achieve a flat and pristine graphite surface. In order to fabricate microscale relief features on the graphite disk, a 1.3  $\mu$ m thick photoresist layer was spun onto the HOPG surface and exposed on an

ABM contact printer. After development, the features were etched into the HOPG using an O2-based RIE recipe with an etching rate of  $\sim$ 50 nm/min. Finally, the photoresist was removed by soaking the HOPG disk in acetone for 10 min. The nanoscale graphitic features were fabricated using electron beam induced deposition (EBID) followed by RIE. A SiO<sub>x</sub> mask was patterned using a Zeiss XB 1540 focused ion beam/SEM etching/deposition system equipped with an XENOS pattern generator. The 15-50 nm wide  $SiO_x$ nanolines were deposited onto the pristine graphite surface irradiated by a 20 keV electron beam. Afterward, the nanoscale graphitic features were etched with the same O<sub>2</sub> plasma recipe with the  $SiO_x$  features acting as the etching mask. Finally, the SiO<sub>x</sub> mask was removed in a diluted hydrofluoric acid solution. The EFEG process was used to exfoliate and print the FLG features onto a Si substrate coated with 50 nm thick SiO<sub>2</sub>, thermally grown in a Tystar oven at 1000 °C. For the exfoliation/printing process, the HOPG template and the SiO<sub>2</sub>/Si substrate were clamped between a pair of homemade parallel plates, and a B&K Precision model 1715 dc power supply (0-50 V) was used to apply voltage between plates. In addition, an atomic scanning microscope (Veeco caliber SPM-AFM) was employed to measure the thickness of exfoliated FLG features in the tapping mode.

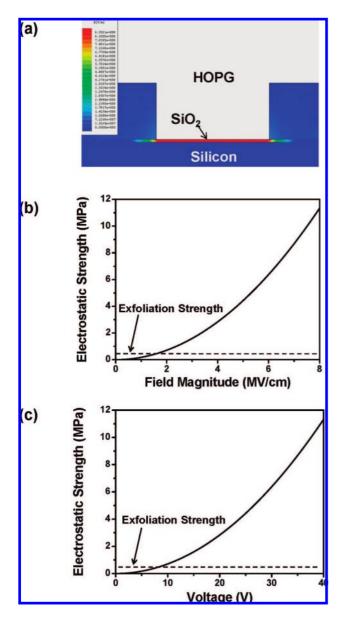

To determine the field strengths needed for performing the EFEG process, the electrostatic exfoliation process was simulated using commercially distributed software (Ansoft Maxwell SV). Figure 2a visualizes the 2D simulation model, in which a graphite template bearing a 1  $\mu$ m diameter, 0.5 μm high pillar is pressed against a silicon substrate coated with 50 nm thick SiO<sub>2</sub>, and a dc voltage is applied between the HOPG template and the silicon substrate. The field distribution and the total electrostatic force were solved using a finite element analysis (FEA). Figure 2b plots the electrostatic strength (megapascals) acting on the graphite surface as a function of the average field magnitude in the SiO<sub>2</sub> layer, which is compared with the exfoliation strength of graphenes that is defined as the minimum stress required for fully separating a graphene monolayer from the bulk graphite ( $\sim$ 0.4 MPa marked by the dashed line).<sup>20-22</sup> Figure 2b indicates that the minimum field magnitude required to exfoliate graphene flakes is  $\sim$ 1.7 MV/cm, which is far below the typical breakdown limit of thermally grown  $SiO_2$  ( $\sim 10$ MV/cm) and thus should not result in electrical damage. Given a SiO<sub>2</sub> thickness of 50 nm, Figure 2c plots the electrostatic strength versus applied voltage, which indicates that the minimum voltage required for graphene exfoliation is about 8.5 V for this particular setup.

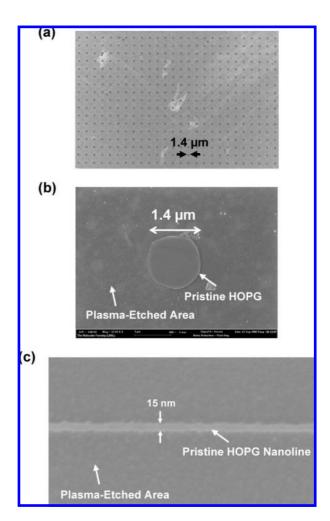

Figure 3 shows scanning electron micrographs (SEMs) of raised microscale and nanoscale features patterned on a HOPG disk by using either photolithography or electron beam induced deposition (EBID) followed with RIE, which include periodic pillars with average diameter of 1.4  $\mu$ m (Figure 3, panels a and b) and 15 nm wide nanolines (Figure 3c). The heights of microscale and nanoscale features are about 0.5  $\mu$ m and 40 nm, respectively. The high-magnification SEMs in panels b and c of Figure 3 display that the

**Figure 2.** (a) A 2D simulation model of EFEG, in which a graphite template bearing a 1  $\mu$ m diameter, 0.5  $\mu$ m high pillar is pressed against a silicon substrate coated with 50 nm thick SiO<sub>2</sub>, and a voltage is applied between the HOPG template and the substrate to create electric field and electrostatic force. The simulation was performed to calculate electrostatic strength acting on the graphite surface as a function of (b) field magnitude in the SiO<sub>2</sub> layer and (c) voltage. The dashed line marks the required exfoliation strength for separating a graphene monolayer from the graphite surface ( $\sim$ 0.4 MPa).

$O_2$ -plasma-etched area has a higher roughness than a pristinie HOPG surface, and this is attributed to the oxidation of graphite surface. <sup>23,24</sup> However, the feature area protected by the etching masks (photoresist or  $SiO_x$ ) is still as smooth as a pristine graphite surface. This should yield a conformal contact with the flat substrate during an EFEG process and therefore a high transfer-printing efficiency of graphene.

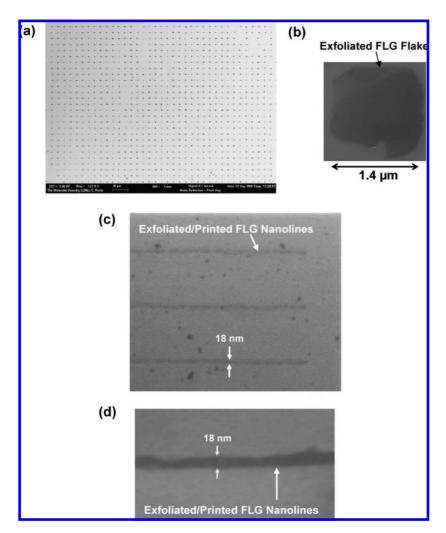

Figure 4 shows the SEMs of microscale and nanoscale FLG features electrically exfoliated and printed on a  $SiO_2$  surface by EFEG. Figure 4a shows a low-magnification SEM of the array of 1.4  $\mu$ m diameter FLG pillars. We attribute the grayscale variation of the graphitic flakes over the large

**Figure 3.** Scanning electron microscopy (SEM) images of relief features prepatterned on a pristine HOPG surface, which include (a) array of 1.4  $\mu$ m diameter pillars, (b) zoomed view of an individual 1.4  $\mu$ m diameter, 0.5  $\mu$ m high pillar, and (c) a 15 nm wide, 40 nm high nanoline. The microscale and nanoscale features were patterned by photolithography and electron-beam-induced deposition (EBID) followed with O<sub>2</sub>-based RIE, respectively.

area to the variation of FLG thickness over the wafer and/or the ripples in the surface of graphene. We analyzed these variations using atomic force microscopy (AFM) which is described subsequently. Figure 4a demonstrates that the EFEG process can exfoliate and print graphitic material over large areas without using any adhesion coating layer, and the exfoliated flake can retain the arrangement and periodicity of the original pattern on the HOPG template. The highmagnification SEM in Figure 4b shows the zoomed view of an exemplary FLG pillar, which shows that most of the area of the flake was conformably adhered to the flat SiO2 surface by electrostatic force despite a partially wrapped edge. We believe this arises due to the interlayer drag force in the graphite during the graphene exfoliation. Figure 4c shows the SEM of 18 nm wide, 1.5  $\mu$ m long graphene nanolines with a spacing of 300 nm printed on the same SiO<sub>2</sub> surface, and Figure 4d shows the zoomed view of an individual 18 nm wide graphene nanoline, which demonstrates that the EFEG process is also capable of directly incorporating nanoscale pre-engineered graphene features (e.g., nanoribbons) into device sites (e.g., transistors). So far the maximum

**Figure 4.** SEM images of exfoliated and printed prepatterned FLG features on a SiO<sub>2</sub>/Si substrate by using EFEG, which include (a) an array of 1.4  $\mu$ m diameter FLG pillars, (b) a zoomed view of an exemplary 1.4  $\mu$ m FLG pillar, (c) 18 nm wide graphene nanolines, and (d) a zoomed view of an individual 18 nm wide graphene nanoline.

SiO<sub>2</sub> area incorporated with graphene is limited by our HOPG disk area, but the EFEG process could be performed in a step-and-repeat fashion to extend the total processing area. In addition, as a control experiment, we performed the transfer-printing of prepatterned FLGs on the same SiO<sub>2</sub> surface without applying the electric field, and we found that the area incorporated with FLG flakes is about 2 orders of magnitude smaller than that generated by EFEG. Therefore, we conclude that the electrostatic force indeed plays a critical role in the exfoliation of graphene features from the HOPG template.

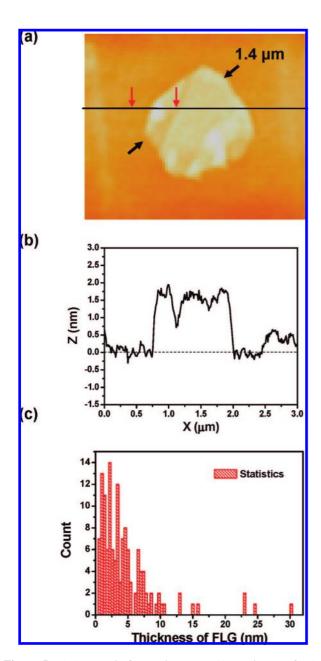

AFM images were obtained to measure the thickness of exfoliated FLG features, and the thickness value was interpreted into the number of graphene monolayers on the basis of the recent work by Nemes-Incze et al. <sup>25</sup> Figure 5a shows the AFM image of an individual 1.4  $\mu$ m wide FLG flake printed on the SiO<sub>2</sub> surface. The AFM image clearly displays a variation of FLG thickness over the whole flake. We pose three possible causes for this variation: (1) the folding or wrapping of graphene edge, (2) the variation of the number of graphene monolayers over the whole FLG flake, and (3) the rippling of the graphene surface generated during the printing/exfoliation course. The scanline denoted

by the solid line and accordingly plotted in Figure 5b explicitly exhibits a variation of FLG thickness from  $t_{\rm min} = 0.72$  nm (1 monolayer) to  $t_{\rm max} = 1.94$  nm (5 monolayers) with an average value of  $t_{\rm avg} = 1.54$  nm (4 monolayers) (standard deviation  $\sigma = 0.25$  nm). Furthermore, the average thickness data of 135 1.4  $\mu$ m wide FLG flakes exfoliated in a single EFEG cycle is presented as a stacked column chart (Figure 5c). Figure 5c shows an interflake variation of the average FLG thickness over the whole printed area ( $\sim 1$  cm²), which ranges from 0.5 nm (1 monolayer) to 30 nm (87 layers) with a most-likely value of  $\sim 2.7$  nm (7 layers), average thickness of 4.5 nm (12 layers) (standard deviation of 3.0 nm).

In order to evaluate the electronic characteristic of FLGs exfoliated and printed with the EFEG process, we fabricated graphene nanoribbon field effect transistors (GFETs) using exfoliated FLG nanolines on SiO<sub>2</sub>/Si substrates. In our specific fabrication, a cross-beam system equipped with a pattern generator was used to deposit platinum finger contacts to define drain/source contacts on FLG nanolines, which also connect the graphene channel with the large metal contact pads (4 nm Cr/75 nm Au), which are fabricated by photolithography followed with lift-off in acetone after the

**Figure 5.** (a) An atomic force microscopy (AFM) image of a 1.4  $\mu$ m diameter FLG flake exfoliated and printed on the SiO<sub>2</sub> surface. The solid line indicates a scanning trace across the flake, which is also plotted in (b). (c) The stacked column chart of the average thickness data collected from 135 exfoliated/printed 1.4  $\mu$ m wide FLG flakes on SiO<sub>2</sub> surface.

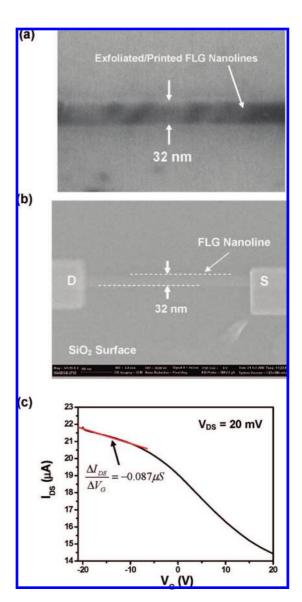

EFEG process. Finally, another metallic contact is made onto the Si substrate, which serves as a back gate contact. Figure 6a shows the SEM of an as-exfoliated 32 nm wide FLG nanoline, which was used to fabricate a back-gated graphene nanoribbon FET with channel length of  $L=0.53~\mu m$  and gate dielectric thickness of d=50 nm, as shown in Figure 6b. The device characteristic curves of this GFET device were measured using an Agilent-4155 semiconductor parameter analyzer. Figure 6c plots the drain—source current ( $I_{DS}$ ) as a function of the gate voltage ( $V_{G}$ ) under a fixed drain—source voltage ( $V_{DS}=20~mV$ ). As shown in Figure 6c, this back-gated graphene nanoribbon FET exhibits a typical gate modulation behavior for the hole-dominated

**Figure 6.** (a) A SEM image of an as-exfoliated 32 nm wide FLG nanoline. (b) A SEM image of a back-gated graphene field-effect transistor with channel width of 32 nm, channel length of  $0.53~\mu m$ , gate dielectric (SiO<sub>2</sub>) thickness of 50 nm, in which platinum finger contacts were deposited as drain and source contacts, and the silicon substrate serves as a back gate. (c) Drain—source current  $I_{\rm DS}$  as a function of gate voltage  $V_{\rm G}$  under a fixed drain—source voltage  $V_{\rm DS} = 20~{\rm mV}$ .

conduction in the range of  $V_{\rm G}$  from  $V_{\rm G}=-20$  to 20 V (field magnitude  $\xi=-4$  to 4 MV/cm), and the curve slope value (or transconductance) at the linear region was obtained to be  $\Delta I_{\rm DS}/\Delta V_{\rm G}=-0.087~\mu{\rm S}$  by the linear fitting (denoted with the red solid line). The hole mobility was subsequently extracted to be  $\mu_{\rm h}=1,050~{\rm cm^2/(V~s)}$  by using eq 1, where  $\varepsilon_0$  is the vacuum permittivity;  $\varepsilon_{\rm r}\sim 3.9$  is the dielectric constant of SiO<sub>2</sub>;  $C_{\rm ox}$  is the gate capacitance; w/L is the width/length ratio of the graphene channel. This hole mobility value is among the highest mobility values reported for few-layer graphenes contacting a supporting material surface 4.5.8.9.15.27 and indicates that the EFEG approach can be used to build nanoscale graphene devices with excellent performance. For our GFETs, we do not observe electron conduction in the range of  $V_{\rm G}$  from -20 to 20 V. The loss

of electron conduction may be attributed to the unexpected contamination of HOPG during the material handling, which may shift the bipolar transition point out of the measurement range. 5,6,8

$$\mu = \frac{\Delta I_{\rm DS}}{C_{\rm ox} \frac{W}{L} V_{\rm DS} \Delta V_{\rm G}} \tag{1}$$

$$C_{\rm ox} = \frac{\varepsilon_0 \varepsilon_{\rm r}}{d}$$

In summary, we developed and demonstrated a novel approach for printing prepatterned few-layer graphenes into the device locations, named as electrostatic-force-assisted exfoliation of few-layer graphenes (EFEG). In this process, the microscale and nanoscale features are prepatterned onto a HOPG disk, which serves as both a template and source of material. When the HOPG template is brought into a conformal contact with a Si substrate coated with SiO<sub>2</sub>, a voltage is applied between HOPG and Si that generates an electrostatic force, which can exfoliate the prepatterned FLG features as the HOPG template is removed. With this approach, we have successfully demonstrated the exfoliation/ printing of FLG features with critical dimensions ranging from 18 nm to 1.4  $\mu$ m. In addition, the electrically printed FLG flakes have been used to build graphene nanoribbon transistors with excellent performance. This novel printing approach does not need any additional adhesion layer and can be repeatedly performed to incorporate graphitic materials over a large area in a parallel fashion.

**Acknowledgment.** This work was supported by the Director, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231.

## References

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Science 2004, 306 (5696), 666–669.

- Avouris, P.; Chen, Z. H.; Perebeinos, V. Nat. Nanotechnol. 2007, 2 (10), 605–615.

- (3) Geim, A. K.; Novoselov, K. S. Nat. Mater. 2007, 6 (3), 183.

- (4) Lemme, M. C.; Echtermeyer, T. J.; Baus, M.; Kurz, H. IEEE Electron Device Lett. 2007, 28 (4), 282–284.

- (5) Gu, G.; Nie, S.; Feenstra, R. M.; Devaty, R. P.; Choyke, W. J.; Chan, W. K.; Kane, M. G. Appl. Phys. Lett. 2007, 90 (25), 253507.

- (6) Liang, X.; Fu, Z.; Chou, S. Y. Nano Lett. 2007, 7 (12), 3840-3844.

- (7) Li, X. L.; Wang, X. R.; Zhang, L.; Lee, S.; Dai, H. J. Science 2008, 319 (5867), 1229–1232.

- (8) Wang, X. R.; Ouyang, Y. J.; Li, X. L.; Wang, H. L.; Guo, J.; Dai, H. J. Phys. Rev. Lett. 2008, 100 (206803),

- (9) Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kin, P.; Shepard, K. L. Nat. Nanotechnol. 2008, 3, 654–659.

- (10) Berger, C.; Song, Z.; Li, T.; Li, X.; Ogbazghi, A. Y.; Feng, R.; Dai, Z.; Marchenkov, A. N.; Conrad, E. H.; First, P. N.; de Heer, W. A. J. Phys. Chem. 2004, 108, 19912–16.

- (11) Berger, C.; Song, Z.; Li, X.; Wu, X.; Brown, N.; Naud, C.; Mayou, D.; Li, T.; Hass, J.; Marchenkov, A. N.; Conrad, E. H.; First, P. N.; de Heer, W. A. Science 2006, 312 (5777), 1191–1196.

- (12) Zhou, S. Y.; Gweon, G.-H.; Fedorov, A. V.; First, P. N.; De Heer, W. A.; Lee, D.-H.; Guinea, F.; Castro Neto, A. H.; Lanzara, A. Nat. Mater. 2007, 6, 770.

- (13) Coraux, J.; N'Diaye, A. T.; Busse, C.; Michely, T. Nano Lett. 2008, 8 (2), 564–570.

- (14) Chen, J.-H.; Ishigami, M.; Jang, C.; Hines, D. R.; Fuhrer, M. S.; Williams, E. D. Adv. Mater. 2007, 19 (21), 3623–3627.

- (15) EDA, G.; Fanchini, G.; Chhowalla, M. Nat. Nanotechnol. 2008, 3, 270–274.

- (16) Stankovicha, S.; Dikina, D. A.; Pinera, R. D.; Kohlhaasa, K. A.; Kleinhammesc, A.; Jiac, Y.; Wuc, Y.; Nguyenb, S. T.; Ruoff, R. S. Carbon 2007, 45 (7), 1558–1565.

- (17) Ouyang, Y.; Yoon, Y.; Fodor, J. K.; Guo, J. Appl. Phys. Lett. 2006, 89 (20).

- (18) Ouyang, Y.; Yoon, Y.; Guo, J. IEEE Trans. Electron Devices 2007, 54 (9), 2223–2231.

- (19) Tapaszto, L.; Dobrik, G.; Lambin, P.; Biro, L. Nat. Nanotechnol. 2008, 3, 397–401.

- (20) Kuzumaki, T.; Sawada, H.; Ichinose, H.; Horiike, Y.; Kizuka, T. Appl. Phys. Lett. 2001, 79 (27), 4580.

- (21) Palser, A. H. R. Phys. Chem. Chem. Phys. 1999, 1, 4459-4464.

- (22) RozpAlocha, F.; Patyka, J.; Stankowskib, J. Acta Phys. Pol., A 2007, 112, 557–562.

- (23) Nakahara, M.; Sanada, Y. J. Mater. Sci. 1994, 29, 3193-3199.

- (24) Lu, X. K.; Huang, H.; Nemchuk, N.; Ruoff, R. S. Appl. Phys. Lett. 1999, 75 (2), 193–195.

- (25) Nemes-Incze, P.; Osvátha, Z.; Kamarásb, K.; Biró, L. P. Carbon 2008, 46 (11), 1435–1442.

- (26) Muller, R. S.; Kamins, T. I.; Chan, M. Device Electronics for Integrated Circuits, 3rd ed.; John Wiley & Sons: New York, 2002; p 431.

- (27) Dayen, J. F.; Mahmood, A.; Golubev, D. S.; Roch-Jeune, I.; Salles, P.; Dujardin, E. Small 2008, 4 (6), 716–720.

NL803512Z